I2C バス — 割り当て、デバイス、データ転送、アドレス指定

電子回路を作成する場合、多くの開発者は、個々のブロックのマッチング、サンプリング、アドレス指定のために多数の中間チップを使用する必要性に直面します。補助チップの数を最小限に抑えるために、フィリップスは 1980 年代に 2 線双方向 I2C シリアル ネットワーク インターフェイスを提案しました。これは、単一デバイス内で複数のチップを管理するように特別に設計されました。

現在、フィリップスだけでも、メモリ、ビデオ プロセッサ システム、アナログ/デジタルおよびデジタル/アナログ コンバータ、ディスプレイ ドライバなど、さまざまな目的の電子機器向けに 100 を超える I2C 互換デバイスを製造しています。

I2C バスは、シリアル データ交換プロトコルを改良したもので、通常の「高速」モードで 100 ~ 400 kbps のレートでシリアル 8 ビット データを送信できます。ここでは、データ交換のプロセスは、データ用の SDA ラインと同期用の SCL ラインの 2 つのワイヤ (共通ワイヤはカウントしません) のみで実装されています。

バスに接続されているデバイスの出力のカスケードにはオープン コレクタまたはチャネルがあり、AND 配線が複製されるため、バスは双方向になります。その結果、バスによってチップ間の接続の数が最小限に抑えられ、ボード上に必要なピンとトレースが少なくなります。その結果、基板自体がよりシンプルで、よりコンパクトになり、生産においてはより技術的に進歩したものになることがわかりました。

このプロトコルを使用すると、アドレス デコーダやその他の外部ネゴシエーション ロジックを無効にすることができます。 I2C バス上で同時に動作できるチップの数は、その容量によって制限されます (最大 400 pF)。

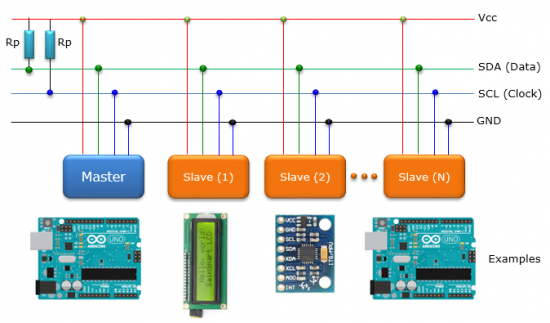

I2C 互換 IC には、強い干渉が存在する場合でもデータの整合性を確保するハードウェア ノイズ抑制アルゴリズムが搭載されています。このようなデバイスには、電源電圧が異なる場合でもマイクロ回路が相互に通信できるようにするインターフェイスが備わっています。以下の図では、共通バスを介して複数のマイクロ回路を接続する原理を理解することができます。

バスに接続された各デバイスは独自の固有のアドレスを持ち、それによって決定され、デバイスの目的に応じて受信機または送信機として機能します。データを送信する場合、これらのデバイスはマスター (マスター) またはスレーブ (スレーブ) になることができます。マスターは、データ転送を開始し、SCL ライン上にクロック信号を生成するデバイスです。マスターとの関係では、スレーブは宛先デバイスです。

I2C バス上での動作のいかなる瞬間においても、マスターとして機能できるデバイスは 1 つだけです。 SCL ラインに信号を生成します。マスターは、マスター受信機またはマスター送信機のいずれかになります。

原則として、バスは複数の異なるマスターを許可しますが、制御信号の形成とバスのステータスの監視の特性に制限を課します。これは、複数のマスターが同時に送信を開始できることを意味しますが、この種の競合は調停、つまりバスが別のマスターによって占有されていることを検出したときのマスターの動作のおかげで排除されます。

デバイスのペアの同期は、すべてのデバイスがバスに接続され、「AND」配線を形成することによって保証されます。最初は、SDA 信号と SCL 信号は High です。

スタートとストップ

交換はマスターが«START» 状態を生成することで始まります。SDA ラインでは信号がハイからロー状態になり、一方、SCL ラインは安定したハイレベルになります。バスに接続されているすべてのデバイスは、この状況を交換を開始するコマンドとして認識します。

各マスターは、バス上でデータを送信するときに、SCL ライン上に個別のクロック信号を生成します。

交換はマスターによる STOP 状態の形成で終了します。SDA ラインでは信号が Low から High に変化しますが、SCL ラインは安定した High レベルになります。

ドライバーは常に START 信号と STOP 信号のソースとして機能します。 «START» 信号が修正されるとすぐに、回線がビジー状態であることを意味します。 STOP 信号が検出されると、ラインはフリーになります。

START 状態を宣言した直後、マスターは SCL ラインを Low に切り替え、最初のメッセージ バイトの最上位ビットを SDA ラインに送信します。メッセージのバイト数には制限がありません。SDA ラインの変更は、SCL ラインの信号レベルが Low の場合にのみ有効になります。データは有効であり、同期パルスが High の場合にのみ変更しないでください。

マスター トランスミッターからのバイトがスレーブ レシーバーによって受信されたことの確認は、8 番目のデータ ビットを受信した後、SDA ライン上に特別なアクノリッジ ビットを設定することによって行われます。

確認

したがって、トランスミッターからレシーバーに 8 ビットのデータを送信すると、受信デバイスの SDA ラインが Low になると、SCL ラインに余分なパルスが発生し、バイト全体を受信したことを示します。

確認はデータ転送プロセスの不可欠な部分です。マスターは同期パルスを生成します。トランスミッタは、アクノリッジクロックがアクティブである間、SDA に Low 状態を送信します。同期パルスが High の間、受信機は SDA を Low に保つ必要があります。

宛先スレーブが、たとえば現在ビジーであるなどの理由でそのアドレスを認識しない場合、データ ラインを High に保持する必要があります。その後、マスターは STOP 信号を送ってディスパッチを中止することができます。

受信がマスター受信機によって実行される場合、最後のバイトを確認することではなく、送信の完了後にスレーブ送信機に通知する義務があります。スレーブトランスミッタはデータラインを解放し、マスタが STOP 信号または繰り返し START 信号を発行できるようにします。

デバイスの同期は、SCL ラインへの接続が「AND」原理に従って行われることによって保証されます。

マスターには、SCL ラインの Low から High への遷移を制御する唯一の権利はありません。スレーブが受信したビットを処理するためにさらに時間が必要な場合は、次のデータ ビットを受信する準備ができるまで独立して SCL を Low に保持できます。このような状況における SCL ラインは、最長のローレベル同期パルスの持続時間の間ローになります。

継続的な低レベルが最も低いデバイスは、長い期間が終了するまでアイドル状態のままになります。すべてのデバイスが Low 同期期間を終了すると、SCL が High になります。

すべてのデバイスはクロック High を開始し、その期間を完了した最初のデバイスが最初に SCL ラインを Low に設定します。その結果、SCL の Low 状態の継続時間は、デバイスの 1 つの同期パルスの最長の Low 状態によって決まり、High 状態の継続時間は、デバイスの 1 つの同期パルスの最短の期間によって決まります。デバイス。

同期信号は、ビットおよびバイト レベルでデータ送信を制御する手段として受信機で使用できます。

デバイスが高速でバイトを受信できるが、受信したバイトを保存するか、次のバイトの受信を準備するのに一定の時間がかかる場合、バイトを受信して確認応答した後も SCL を Low に保持し続ける可能性があり、送信機がスタンバイ状態になります。

ビットレベルなどのハードウェア回路が組み込まれていないマイクロコントローラは、ロー状態の継続時間を長くすることでクロック速度を遅くすることができ、その結果、マスターデバイスのボーレートはデバイスの速度によって決まります。遅いデバイス。

アドレッシング

I2C バスに接続された各デバイスには固有のプログラム アドレスがあり、マスターは特定のコマンドを送信することでそのデバイスをアドレス指定します。同じタイプのマイクロ回路は、セレクターのデジタル入力の形式またはアナログ形式のいずれかで実装されるアドレス セレクターによって特徴付けられます。アドレスは、バスに接続されているデバイスのアドレス空間に分割されます。

通常モードは 7 ビットのアドレス指定を想定しています。アドレス指定は次のように機能します。«START» コマンドの後、マスターは最初のバイトを送信し、マスターと通信するためにどのスレーブ デバイスが必要かを決定します。バス上のすべてのデバイスを定義する共通の呼び出しアドレスもあり、すべてのデバイスが (理論的には) 確認応答でそれに応答しますが、実際にはこれはまれです。

したがって、最初のバイトの最初の 7 ビットはスレーブ アドレスです。最下位ビットの 8 番目は、データの送信方向を示します。 «0» がある場合、情報はマスターからこのスレーブに書き込まれます。 «1» の場合、情報はマスターによってこのスレーブから読み取られます。

マスターがアドレス バイトの送信を完了すると、各スレーブはそのアドレスをマスターと比較します。同じアドレスを持つ人は誰でもスレーブであり、アドレス バイトの最下位ビットの値に応じてスレーブ送信機またはスレーブ受信機として定義されます。

スレーブ アドレスには、固定部分とプログラム可能な部分を含めることができます。多くの場合、同じタイプの多数のデバイスが 1 つのシステムで動作し、アドレスのプログラム可能な部分により、バス上で最大数の同じタイプのデバイスを使用できるようになります。プログラム可能なアドレス バイトのビット数は、チップ上の空きピンの数によって異なります。

場合によっては、プログラマブルなアドレス範囲のアナログ設定を備えたピンで十分な場合があります。たとえば、まさにそのような実装を備えた LED インジケータードライバーである SAA1064 です。特定のピンの電位によってチップのアドレス空間のオフセットが決定されるため、同じタイプのチップが同じバス上で動作する際に競合が発生しません。 I2C バスをサポートするすべてのチップには、メーカーがドキュメントで指定する一連のアドレスが含まれています。

«11110XX» の組み合わせは 10 ビットのアドレス指定用に予約されています。 «START» コマンドから «STOP» コマンドへのデータの交換を想像すると、次のようになります。

ここでは、単純なデータ交換フォーマットと結合されたデータ交換フォーマットが許可されます。結合フォーマットは、«START» と «STOP» の間でマスターとスレーブが受信機および送信機として機能できることを意味します。これは、シリアル メモリ管理などに役立ちます。

データの最初のバイトでメモリ アドレスを転送します。次に、«START» コマンドを繰り返してスレーブアドレスを読み取ると、メモリデータが機能します。以前にアクセスしたアドレスを自動的にインクリメントまたはデクリメントする決定は、チップのドキュメントを事前に検討した後、デバイス開発者によって行われます。いずれにせよ、START コマンドを受信した後、すべてのデバイスはロジックを復元し、アドレスに名前が付けられるように準備する必要があります。