電界効果トランジスタ

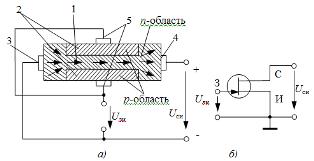

電界効果 (ユニポーラ) トランジスタは、制御 pn 接合 (図 1) を備えたトランジスタと絶縁ゲートを備えたトランジスタに分けられます。制御pn接合を備えた電界効果トランジスタのデバイスは、バイポーラトランジスタよりも単純です。

電界効果 (ユニポーラ) トランジスタは、制御 pn 接合 (図 1) を備えたトランジスタと絶縁ゲートを備えたトランジスタに分けられます。制御pn接合を備えた電界効果トランジスタのデバイスは、バイポーラトランジスタよりも単純です。

n チャネル トランジスタでは、チャネル内の主な電荷キャリアは電子であり、チャネルに沿って低電位のソースから高電位のドレインまで移動し、ドレイン電流 Ic を形成します。 FET のゲートとソースの間に逆電圧が印加され、チャネルの n 領域とゲートの p 領域によって形成される p-n 接合がブロックされます。

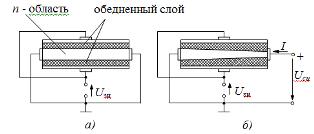

したがって、n チャネル FET では、印加電圧の極性は次のようになります: Usi > 0、Usi ≤ 0。ゲートとチャネル間のpn接合にブロッキング電圧が印加されると(図2aを参照)、電荷キャリアが空乏化した高抵抗の均一な層がチャネル境界に現れます。

米。 1. pn 接合の形のゲートと n 型チャネルを備えた電界効果トランジスタの構造 (a) と回路 (b)。 1、2 — チャネルおよびポータル ゾーン。 3、4、5 — ソース、ドレイン、刑務所の結論

米。 2. Usi = 0 (a) および Usi> 0 (b) での電界効果トランジスタのチャネル幅

これにより、導電チャネルの幅が減少します。ソース・ドレイン間に電圧を印加すると、空乏層が不均一になり(図2b)、ドレイン付近のチャネル断面積が減少し、チャネルの導電率も低下します。

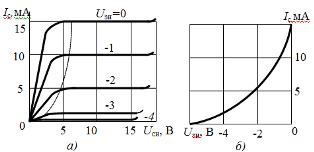

FETのVAH特性を図に示します。 3. ここで、一定のゲート電圧 Uzi におけるドレイン電流 Ic の電圧 Usi に対する依存性が、電界効果トランジスタの出力またはドレイン特性を決定します (図 3、a)。

米。 3. 電界効果トランジスタの出力 (a) および伝達 (b) の電圧-電流特性。

特性の初期部分では、Umi が増加するにつれてドレイン電流が増加します。ソース・ドレイン間電圧が Usi = Uzap – [Uzi] まで増加すると、チャネルがオーバーラップし、電流 Ic のさらなる増加は停止します (飽和領域)。

負のゲート・ソース間電圧 Uzi では、チャネルがオーバーラップする電圧 Uc と電流 Ic の値が低くなります。

電圧 Usi がさらに増加すると、ゲートとチャネル間の p-n 接合が破壊され、トランジスタが無効になります。出力特性を使用して、伝達特性 Ic = f (Uz) を構築できます (図 3、b)。

飽和セクションでは、実質的に電圧 Usi から独立しています。これは、入力電圧 (ゲート - ドレイン) が存在しない場合、チャネルが特定の導電率を持ち、初期ドレイン電流 Ic0 と呼ばれる電流が流れることを示しています。

チャネルを効果的に「ロック」するには、入力に遮断電圧 Uotc を印加する必要があります。FET の入力特性 (ゲート ソース電圧に対するゲート ドレイン電流 I3 の依存性) は、Uzi < 0 ではゲートとチャネル間の p-n 接合が閉じられ、ゲート電流が減少するため、通常は使用されません。非常に小さいため (I3 = 10-8 … 10-9 A)、多くの場合無視できます。

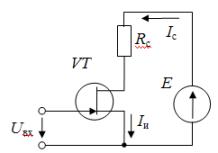

この場合のように バイポーラトランジスタ、フィールドには、共通のゲート、ドレイン、ソースを備えた 3 つのスイッチング回路があります (図 4)。制御用pn接合を備えた電界効果トランジスタのI-V伝達特性を図に示します。 3、b.

米。 4. 制御用pn接合を備えたソース接地電界効果トランジスタのスイッチング方式

バイポーラトランジスタと比較した制御pn接合を備えた電界効果トランジスタの主な利点は、高入力インピーダンス、低ノイズ、製造の容易さ、完全にオープンしたチャネルでの電圧降下が低いことですが、電界効果トランジスタには次のような欠点があります。 I の負の領域、つまり V 特性で動作する必要があるため、スキームが複雑になります。

技術科学博士、L.A. ポタポフ教授