アンチエイリアシングフィルターと電圧安定化装置

平滑フィルタは、整流された電圧リップルを低減するように設計されています。リップル平滑化は平滑化係数 q によって評価されます。

平滑フィルタは、整流された電圧リップルを低減するように設計されています。リップル平滑化は平滑化係数 q によって評価されます。

平滑フィルタの主な要素はコンデンサです。 インダクタ 直流と交流で抵抗値が異なるトランジスタもあります。

フィルタ要素のタイプに応じて、容量性フィルタ、誘導性フィルタ、および電子フィルタが区別されます。フィルタリング リンクの数に応じて、フィルタはシングルリンクとマルチリンクに分けられます。

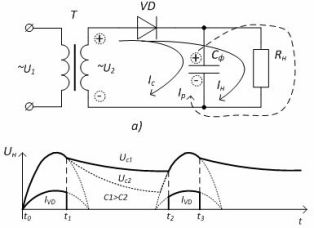

容量性フィルタは、負荷抵抗Rnと並列に接続される大容量のコンデンサです。コンデンサは、高い DC 抵抗と低い AC 抵抗を持っています。半波整流回路を例にフィルターの動作を考えてみましょう(図1、a)。

図 1 - 容量性フィルタを備えた単相半波整流器: a) 回路 b) 動作のタイミング図

t0~t1の時間内に正の半波が流れると(図2.63のb)、負荷電流(ダイオード電流)とコンデンサの充電電流が流れます。コンデンサが充電され、時刻 t1 でコンデンサの電圧が二次巻線の電圧降下を超えます。ダイオードが閉じ、時間間隔 t1 から t2 の間、コンデンサの放電によって負荷に電流が供給されます。チェ。負荷の電流は常に流れるため、整流された電圧のリップルが大幅に減少します。

コンデンサ Cf の静電容量が大きいほど、励起は小さくなります。これは、コンデンサの放電時間、つまり放電時定数 τ = СfRн によって決まります。 τ> 10 では、平滑化係数は式 q = 2π fc m Cf Rn によって決定されます。ここで、fc はネットワークの周波数、m は整流された電圧の半周期の数です。

低負荷電力では、高抵抗の RH 負荷抵抗を備えた容量性フィルタを使用することをお勧めします。

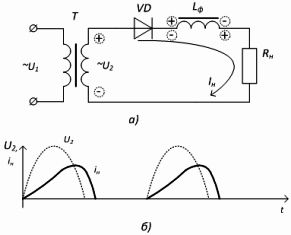

インダクティブフィルター(チョーク) はRnと直列に接続されています(図3、a)。インダクタンスは、DC 抵抗が低く、AC 抵抗が高くなります。リップル平滑化は自己誘導現象に基づいており、最初は電流の増加を防ぎ、その後電流の減少をサポートします(図2、b)。

図 2 - 誘導フィルタを備えた単相半波整流器: a) 回路、b) 動作のタイミング図

誘導フィルタは、中出力および高出力の整流器、つまり大きな負荷電流で動作する整流器に使用されます。

平滑化係数は次の式で決定されます: q = 2π fs m Lf / Rn

容量性および誘導性フィルタの動作は、ネットワークによって消費される電流が流れている間、コンデンサとインダクタがエネルギーを蓄積し、ネットワークからの電流がなくなるか、電流が減少すると、要素がエネルギーを与えるという事実に基づいています。蓄積されたエネルギーをシャットダウンし、負荷の電流 (電圧) を維持します。

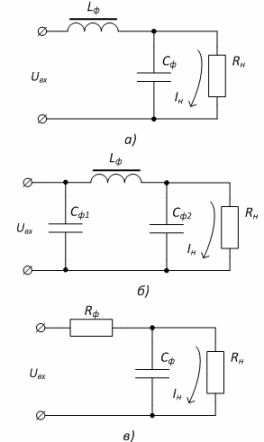

多接合フィルタは、コンデンサとインダクタの両方の平滑特性を使用します。低電力整流器では、負荷抵抗器の抵抗値が数 kOhm である場合、チョーク Lf の代わりに抵抗器 Rf が組み込まれ、これによりフィルタの質量と寸法が大幅に削減されます。

図 3 に LC および RC ラダー フィルタの種類を示します。

図 3 - 多接合フィルター: a) L 字型 LC、b) U 字型 LC、c) RC フィルター

スタビライザーは、主電源電圧の変動や負荷が消費する電流の変化中に、負荷の定電圧 (電流) を安定させるように設計されています。

安定器は、電圧安定器と電流安定器、およびパラメトリック安定器と補償安定器に分けられます。出力電圧の安定性は安定化係数 Kst によって評価されます。

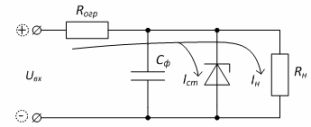

非線形特性を持つ素子である半導体ツェナーダイオードの使用に基づいたパラメトリックスタビライザーであり、デバイスを流れる逆電流が大きく変化しても、ツェナーダイオードの電圧はほぼ一定です。

パラメトリック安定化回路を図 4 に示します。入力電圧 UBX は、制限抵抗 Rlim、並列接続されたツェナー ダイオード VD、および負荷抵抗 Rn の間に分配されます。

図 4 — パラメトリックスタビライザー

入力電圧が増加すると、ツェナーダイオードを流れる電流が増加します。これは、制限抵抗を流れる電流が増加し、その両端でより大きな電圧降下が発生することを意味しますが、負荷電圧は変化しません。

パラメトリックスタビライザーの Kst は 20 ~ 50 程度です。このタイプの安定化装置の欠点は、安定化電流が低いことと効率が低いことです。

パラメトリック スタビライザは、負荷電流が小さい場合 (数百ミリアンペア以下) に、補助電圧源として使用されます。

補償スタビライザーは、トランジスタの可変抵抗を制限抵抗として使用します。入力電圧が増加するとトランジスタの抵抗も増加し、それに応じて電圧が減少すると抵抗も減少します。この場合、負荷の電圧は変化しません。

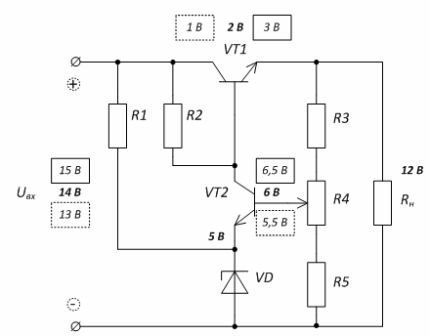

トランジスタの安定化回路を図 5 に示します。出力電圧 URn の調整原理は、調整トランジスタ VT1 の導電率の変化に基づいています。

図5 — 補償電圧レギュレータの回路図

トランジスタVT2には電圧比較回路とDCアンプが組み込まれています。測定回路R3、R4、R5はベース回路に含まれ、基準電圧源R1VDはエミッタ回路に含まれます。

たとえば、入力電圧が増加すると出力も増加し、これによりトランジスタ VT2 のベースの電圧が増加しますが、同時にエミッタ VT2 の電位は同じままになります。これにより、ベース電流が増加し、したがってトランジスタ VT2 のコレクタ電流が増加します。トランジスタ VT1 のベース電位が減少し、トランジスタが閉じて、より大きな電圧降下が発生し、出力電圧が低下します。変わらないまま。

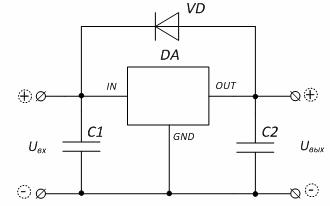

現在、安定化装置は集積回路の形で製造されています。統合スタビライザーをオンにする一般的なスキームを図 6 に示します。

図 6 — 内蔵電圧安定器をオンにするための一般的な回路図

スタビライザーマイクロ回路の出力の指定: «IN» — 入力、«OUT» — 出力、«GND» — コモン (ケース)。スタビライザーが調整可能な場合は、出力«ADJ» — 調整があります。

スタビライザの選択は、出力電圧の値、最大負荷電流、入力電圧の変動範囲に基づいて行われます。