デジタル デバイス: パルス カウンタ、エンコーダ、マルチプレクサ

パルスカウンター — 入力に加えられるパルスの数をカウントするように設計された電子デバイス。受信パルス数を2進数で表現します。

パルスカウンター — 入力に加えられるパルスの数をカウントするように設計された電子デバイス。受信パルス数を2進数で表現します。

パルス カウンタはレジスタ (カウント レジスタ) の一種で、それぞれフリップフロップと論理ゲートで構築されます。

カウンタの主な指標は、カウンタ係数 K 2n、つまりカウンタによってカウントできるパルスの数です。たとえば、4 トリガー カウンタの最大カウント係数は 24 = 16 です。4 トリガー カウンタの場合、最小出力コードは 0000、最大出力コードは -1111 で、カウント係数が Kc = 10 の場合、出力はコード 1001 = 9 になるとカウントを停止します。

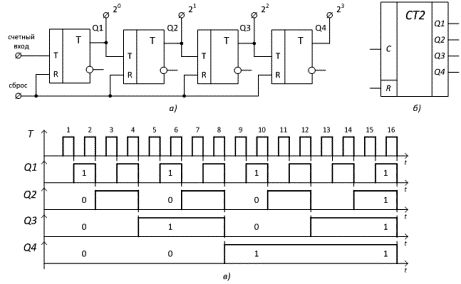

図 1a は、直列に接続された 4 ビット T フリップ カウンタの図を示しています。カウント パルスは、最初のフリップフロップのカウント入力に適用されます。後続のフリップフロップのカウンタ入力は、前のフリップフロップの出力に接続されます。

図 1a は、直列に接続された 4 ビット T フリップ カウンタの図を示しています。カウント パルスは、最初のフリップフロップのカウント入力に適用されます。後続のフリップフロップのカウンタ入力は、前のフリップフロップの出力に接続されます。

回路の動作は、図 1 の b に示すタイミング グラフで示されています。最初のカウントパルスが減衰に達すると、最初のフリップフロップは状態 Q1 = 1 になります。カウンタのデジタル コードは 0001 です。2 番目のカウンタ パルスの終わりに、最初のフリップフロップは状態 «0» になり、2 番目のフリップフロップは状態 «1» になります。カウンタはコード 0010 の番号 2 を記録します。

図 1 — バイナリ 4 桁カウンタ: a) 図、b) 従来のグラフ表現、c) 動作のタイミング図

図(図1、b)から、たとえば、5番目のパルスの減衰に従って、コード0101がカウンタに書き込まれ、9番目のパルスに従ってコード0101が書き込まれ、以下同様であることがわかります。 15 番目のパルスの終わりに、カウンタのすべてのビットが状態「1」に設定され、16 番目のパルスの減衰後にすべてのトリガがリセットされます。つまり、カウンタは初期状態に戻ります。カウンタを強制的にリセットするための«reset»入力があります。

バイナリカウンタのカウント係数は、比 Ksc = 2n から求められます。ここで、n はカウンタのビット (フリップフロップ) の数です。

パルス数をカウントすることは、デジタル情報処理装置で最も一般的な操作です。

バイナリカウンタの動作中、後続の各フリップフロップの出力におけるパルスの繰り返し率は、その入力パルスの周波数と比較して半分に減少します(図1、b)。したがって、カウンタは分周器としても使用されます。

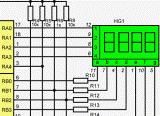

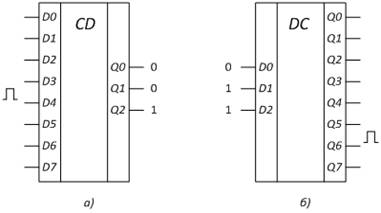

スクランブラー (エンコーダーとも呼ばれる) は、信号をデジタル コード (ほとんどの場合 2 進数系の 10 進数) に変換します。

エンコーダには、10 進数 (0、1、2、…、m — 1) で連続番号が付けられた m 個の入力と n 個の出力があります。入力と出力の数は、2n = m の関係によって決まります (図 2、a)。記号«CD»は、英語のCoderの文字から形成されています。

入力の 1 つに信号を適用すると、出力は入力数値に対応する n ビットの 2 進数を生成します。たとえば、パルスが 4 番目の入力に印加されると、デジタル コード 100 が出力に表示されます (図 2、a)。

デコーダー (デコーダーとも呼ばれる) は、2 進数を小数の 10 進数に変換するために使用されます。デコーダの入力 (図 2、b) は 2 進数を供給することを目的としており、出力には 10 進数で連続した番号が付けられます。 2 進数が入力に適用されると、入力番号に対応する番号を持つ特定の出力に信号が表示されます。たとえば、コード 110 が指定された場合、信号は 6 番目の出力に表示されます。

図 2 — a) UGO エンコーダ、b) UGO デコーダ

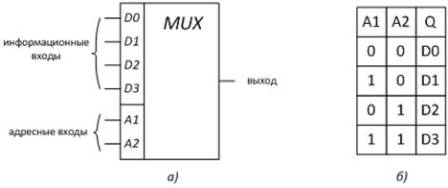

マルチプレクサ - アドレス コードに従って、出力が入力の 1 つに接続されるデバイス。チェ。マルチプレクサは電子スイッチまたは整流子です。

図 3 — マルチプレクサ: a) 従来のグラフィック表現、b) 状態テーブル

アドレス コードは入力 A1、A2 に送信され、どの信号入力がデバイスの出力に送信されるかを決定します (図 3)。

情報をデジタルからアナログに変換するには、デジタル - アナログ コンバーター (DAC) を使用し、逆変換には、アナログ - デジタル コンバーター (ADC) を使用します。

DAC の入力信号は 2 進多桁数で、出力信号は基準電圧に基づいて形成された電圧 Uout です。

アナログデジタル変換手順(図4)は、時間サンプリング(サンプリング)とレベル量子化の2つの段階で構成されます。サンプリング プロセスは、離散時間でのみ連続信号の値を測定することで構成されます。

図 4 - アナログからデジタルへの変換プロセス

量子化では、入力信号の変動範囲が等間隔、つまり量子化レベルに分割されます。この例では 8 つありますが、通常はさらに多くなります。量子化操作は、サンプル値が落ちた間隔を決定し、出力値にデジタル コードを割り当てることに簡略化されます。