デジタルデバイス: フリップフロップ、コンパレータ、レジスタ

デジタル デバイスは論理要素に基づいて構築されているため、論理代数の法則に従います。論理デバイスと同様にデジタル テクノロジーの基本デバイスはフリップフロップです。

デジタル デバイスは論理要素に基づいて構築されているため、論理代数の法則に従います。論理デバイスと同様にデジタル テクノロジーの基本デバイスはフリップフロップです。

トリガー(英語のトリガー - トリガー) - 2 つの安定した状態を持ち、外部インパルスの影響下で 1 つの状態から別の状態にジャンプできる電子デバイス。

トリガー、より正確にはトリガー システムは、2 つの安定状態のいずれかを長期間維持し、外部信号の影響下でそれらを切り替える機能を備えた大きなクラスの電子デバイスと呼ばれます。各トリガ条件は出力電圧値によって簡単に認識できます。

各トリガー状態は、特定の (高または低) 出力電圧レベルに対応します。

1) トリガーは 1 つの状態 (レベル «1») に設定されます。

2) フリップフロップがリセットされ、出力がレベル「0」になります。

定常状態は必要な限り維持され、外部パルスまたは電源電圧をオフにすることによって変更できます。チェ。フリップフロップは、情報の最小単位 (1 ビット) «0» または «1» を保存できる基本的なメモリ要素です。

フリップフロップは、個別の要素、論理要素、集積回路上に構築することも、集積回路の一部として構築することもできます。

フリップフロップの主なタイプには、RS-フリッパー、D-フリッパー、T-フリッパー、JK フリッパーなどがあります。さらに、フリップフロップは非同期と同期に分類されます。非同期作動では、ある状態から別の状態への切り替えは、情報入力への信号の到着とともに直接行われます。データ入力に加えて、同期フリップフロップにはクロック入力があります。それらのスイッチングは、イネーブルクロックパルスが存在する場合にのみ行われます。

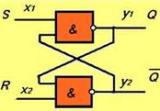

RS トリガーには少なくとも 2 つの入力があります: S (セット — セット) — トリガーはレベル «1» の状態に設定され、R (リセット) — トリガーはレベル «0» の状態にリセットされます。 (図1)。

入力 C が存在すると、フリップフロップは同期します。フリップフロップのスイッチング (出力の状態の変化) は、入力 C に同期 (同期) パルスが到着した瞬間にのみ発生します。

図 1 — RS フリップフロップの従来のグラフィック表現と結論の目的 a) 非同期、b) 同期

直接出力に加えて、フリップフロップは信号が逆になる反転出力を持つこともできます。

表 1 は、フリップフロップが動作中に取り得る状態を示しています。この表は、特定の時刻 tn における入力信号 S および R の値と、次の信号が到着した後の次の時刻 tn + 1 におけるフリップフロップ (直接出力の) の状態を示しています。パルス。新しいトリガー状態は、Q n の前の状態にも影響されます。

チェ。トリガー«1»に書き込む必要がある場合はS入力にパルスを与え、«0»の場合はR入力にパルスを送信します。

S = 1、R = 1 の組み合わせは、出力でどのような状態が確立されるかを予測できないため、禁止された組み合わせです。

表 1 - 同期 RS フリップフロップの状態テーブル

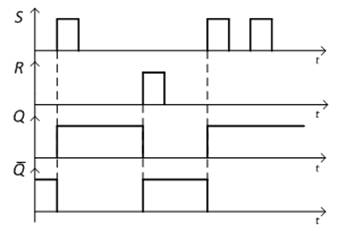

フリップフロップの動作は、タイミング図を使用して確認することもできます (図 2)。

図 2 — 非同期 RS フリップフロップのタイミング図

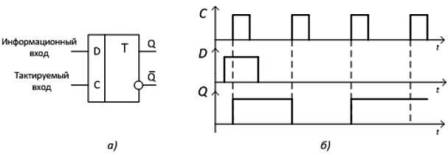

D トリガー (英語の遅延 — 遅延に由来) には、1 つの情報入力と 1 つのクロック (同期) 入力があります (図 3)。

D フリップフロップは、クロック パルス C の到着時にデータ入力 D にあった信号を出力 Q に保存します。フリップフロップは、C = 1 のときに書き込まれた情報を保存します。

表 2 - D フリップフロップの状態の表

図 3 — D トリガー: a) 従来のグラフィック表現、b) 動作のタイミング図

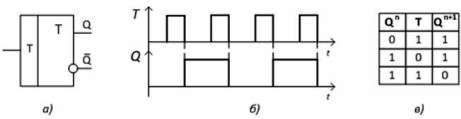

計数フリップフロップとも呼ばれる T トリガー (英語のタンブル、ひっくり返す、宙返りに由来) には、1 つの情報入力 T があります。T 入力 (計数入力) の各パルス (パルス減衰) によって、トリガーが反対の状態に切り替わります。

図 4 は、T トリガーのシンボル (a) と動作のタイミング図 (b) を示しています。

図 4-T フリップフロップ a) 従来のグラフィック表記、b) 動作のタイミング図、c) 状態テーブル

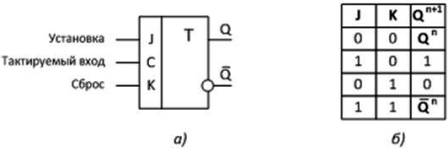

JK トリガー (英語のジャンプ、ジャンプ、キール、ホールドに由来) には、2 つのデータ入力 J および K と、クロック入力 C があります。ピン J および K の割り当ては、ピン R および S の割り当てと似ていますが、トリガーには禁止された組み合わせはありません。 J = K = 1 の場合、状態は反対に変化します (図 5)。

入力を適切に接続すると、トリガーは RS、D、T トリガーの機能を実行できます。普遍的なトリガーです。

図 5 -JK フリップフロップ a) 従来の -グラフィック表記、b) 省略された状態テーブル

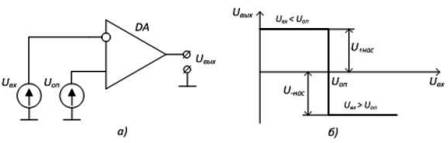

コンパレータ (比較 — 比較) — 2 つの電圧を比較するデバイス — 入力 Uin を基準 Uref と比較します。基準電圧は正または負の極性を持つ定電圧であり、入力電圧は時間の経過とともに変化します。オペアンプに基づく最も単純なコンパレータ回路を図 6 の a に示します。出力 U で Uin Uop の場合 — us (図 6、b)。

図 6 — オペアンプ コンパレータ: a) 最も単純なスキーム b) 性能特性

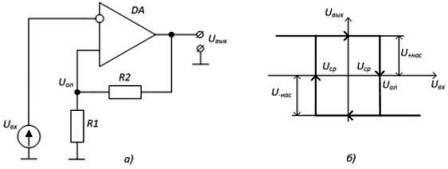

正帰還コンパレータはシュミットトリガと呼ばれます。コンパレータが同じ電圧で«1»から«0»に、またはその逆に切り替わる場合、シュミットトリガは異なる電圧で切り替わります。基準電圧は PIC 回路 R1R2 を作成し、入力信号はオペアンプの反転入力に供給されます。図 7 の b は、シュミット トリガの伝達特性を示しています。

OS のインベントリ入力が負の電圧の場合、Uout = U + sat。これは、正の電圧が非反転入力に作用することを意味します。入力電圧が増加すると、電流 Uin > Uneinv になります。 (Uav — トリガー) コンパレータは状態 Uout = U -sat になります。負の電圧が非反転入力に印加されます。したがって、入力電圧が低下すると、Uin<Uneinvになります。 (Uav — トリガー) コンパレータは状態 Uout = U + sat になります。

図 7 — オペアンプのシュミット動作: a) 最も単純な方式 b) 性能特性

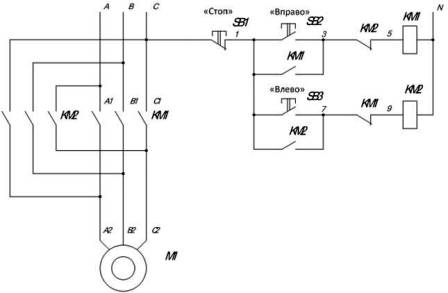

例。図 8 は、電気モーターを制御して始動、停止、逆転を可能にするリレーコンタクターの回路図を示しています。

図8 — リレーコンタクタモータ制御方式

電気モーターの転流は磁気スターター KM1、KM2 によって実行されます。自由に閉じられる接点 KM1、KM2 は、電磁スタータの同時動作を防ぎます。自由に開く接点 KM1、KM2 により、ボタン SB2 および SB3 がセルフロックされます。

動作の信頼性を向上させるためには、リレー・コンタクタの制御回路や電源回路を半導体素子やデバイスを用いた非接触システムに置き換える必要があります。

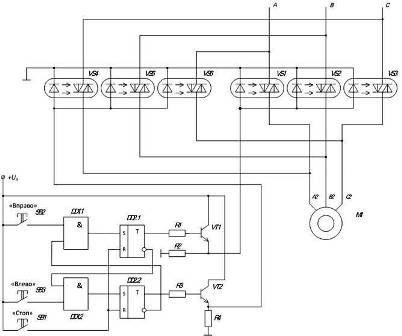

図9に非接触モータ制御回路を示します。

磁気スタータの電源接点はオプトシミスタに置き換えられました: KM1-VS1-VS3、KM2-VS4-VS6。オプトシミスタを使用すると、低電流制御回路を強力な電源回路から分離することができます。

トリガーにはセルフロック ボタン SB2、SB3 が備わっています。ロジック要素と、磁気スターターの 1 つだけが同時に作動することを保証します。

トランジスタ VT1 が開くと、第 1 グループのオプトシミスタ VS1 ~ VS3 の LED に電流が流れ、モータ巻線を流れる電流が確保されます。トランジスタ VT2 が開くと、第 2 グループのオプトシミスタ VS4 に電流が供給されます。 -VS6、電気モーターの逆方向の回転を保証します。

図9|非接触モータ制御回路

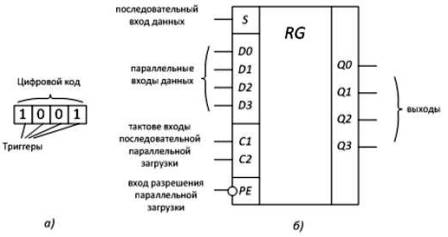

レジスタ - 複数桁の 2 進数の短期間の保存と変換のために設計された電子デバイス。レジスタはフリップフロップで構成されており、フリップフロップの数によって、レジスタが格納できる 2 進数のビット数、つまりレジスタのサイズが決まります (図 10、a)。ロジック要素を使用して、トリガーの操作を整理できます。

図 10 — レジスタ: a) 一般的な表現、b) 従来のグラフィック表記

情報の入出力の方式により、レジスタはパラレルとシリアルに分けられます。

シーケンシャル レジスタでは、フリップフロップが直列に接続されます。つまり、前のフリップフロップの出力が次のフリップフロップの入力に情報を渡します。フリップフロップのクロック入力 C は並列に接続されています。このようなレジスタには 1 つのデータ入力と 1 つの制御入力 (クロック入力 C) があります。

並列レジスタは、4 つのデータ入力があるフリップフロップに同時に書き込みます。

図 10 に、UGO と 4 ビット パラレル/シリアル レジスタのピン割り当てを示します。